_ Department of Integrated Circuits (ASIC)

( ASIC integrated circuits) and explanation of "momentary error" (glitch) in logical blocks (please pay more attention to this matter)

Researcher and author: Dr. ( Afshin Rashid)

Note: In fact, most ASICs use programmable logic blocks, although ASICs have the potential to be faster and may have the advantages of lower power consumption, less electromagnetic interference, and modularity . Better to be in large systems.

( ASIC integrated circuits) are an active area of research in the design of logic circuits. Without the use of sequential logic, computer processing will not be possible. Sequential logic makes possible the use of memory in systems.

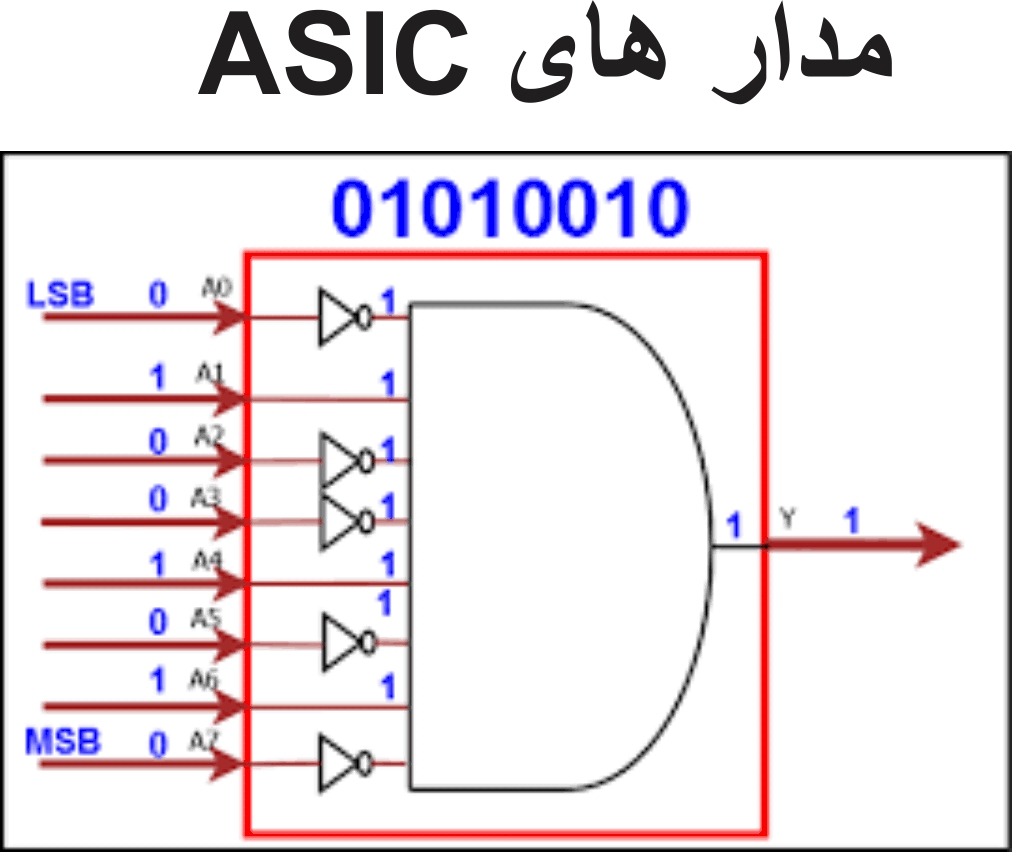

The output ( ASIC integrated circuits) is generated after a specified delay. The amount of this delay depends on many factors, including the manufacturing process of the used components, the temperature of the silicon and the complexity of the circuit. If the final output of a circuit depends on the results of two other integrated circuits and these results are prepared at different times (which in reality happens), ( ASIC integrated circuits) will experience a "glitch" and in The result may not be consistent output according to the intended operation.

( ASIC Programmable Integrated Circuits ) with fixed functionality first parses incoming packets before processing them through a fixed pipeline of logic and various application protocol tables. That is, the ASIC supports a limited set of network protocols that forward packets based on specific rules and forwarding tables. For some switch applications, it is possible that many of the ASIC's supported protocol features will remain unused, and furthermore, any need to accommodate new protocols will require a complete hardware upgrade. It is this inflexibility and inefficiency of fixed-function ASICs that programmable switch ASICs seek to address.

Compared to fixed-function ASICs, ASIC programmable switches are designed based on the protocol-independent switch architecture of its internal memory . With the built-in memory protocol architecture , each step of the memory command line is undefined and requires programming for packet parsing and transport logic for specific matching functions. Switch ASIC programming uses a high-level language called P4, which was developed as an alternative to fixed-function switching. The Open Network Foundation has defined the P4 language as a standard and is driving development through an active and growing P4 community. The development of P4, as well as other packet processing programming languages, allows the data plane to be fully programmable and largely independent of the underlying hardware.

Researcher and author: Dr. ( Afshin Rashid)

Specialized doctorate in nano-microelectronics