_ بخش مدار های مجتمع (Asic _ ای سیک)

(مدارهای مجتمع ASIC _ ای سیک) و تشریح «خطای لحظهای» (glitch) در بلوک های منطقی _ ( لطفاً بر روی این مطلب بیشتر توجه نمایید)

پژوهشگر و نویسنده: دکتر ( افشین رشید)

نکته : در واقع بیش تر (مدارهای مجتمع ASIC) از بلوک های منطقی قابل برنامه ریزی استفاده می کنند اگر چه (مدارهای مجتمع ASIC) پتانسیل سریع تر بودن را دارند و ممکن است دارای مزایای مصرف انرژی کم تر، تداخل الکترومغناطیسی کم تر و ماژولار بهتر در سیستم های بزرگ باشند.

(مدارهای مجتمع ASIC) یک حوزهٔ فعال تحقیق در طراحی مدار های منطقی هستند.بدون استفاده از منطق ترتیبی، پردازش های کامپیوتری امکان پذیر نخواهد بود. منطق ترتیبی استفاده از حافظه را در سیستم ها ممکن می کند.

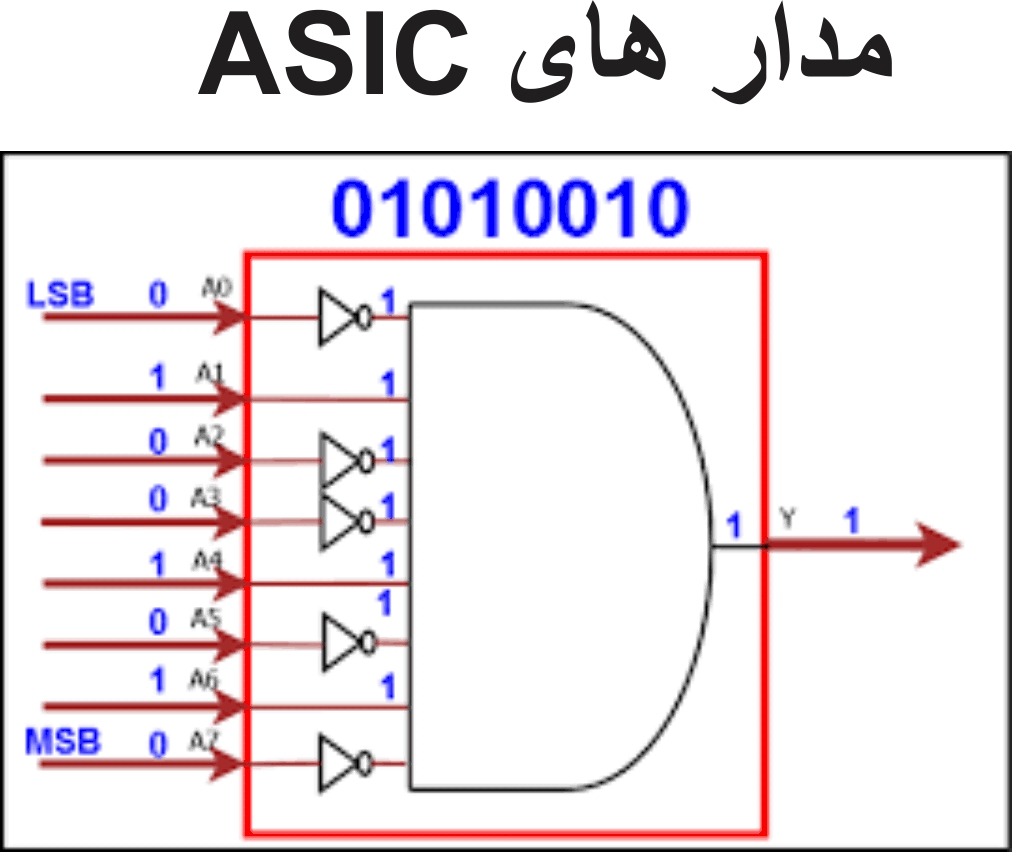

خروجی (مدارهای مجتمع ASIC) پس از یک تأخیر مشخص تولید می شود. مقدار این تأخیر به عوامل بسیار زیادی از جمله فرآیند ساخت قطعات مورد استفاده، دمای سیلیکون و پیچیدگی مدار بستگی دارد. اگر خروجی نهایی یک مدار به نتایج دو مدار ترکیبی دیگر وابسته باشد و این نتایج در زمان های متفاوتی آماده شوند (که در واقعیت همین موضوع اتفاق میافتد)، (مدارهای مجتمع ASIC) دچار یک «خطای لحظهای» (glitch) می شود و در نتیجه ممکن است خروجی ثابتی مطابق با عملیات مورد نظر نداشته باشد.

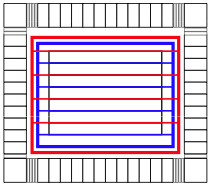

(مدارهای مجتمع قابل برنامه ریزی ASIC) با عملکرد ثابت ابتدا بسته های دریافتی را قبل از پردازش از طریق یک خط لوله ثابت از منطق و جداول مختلف پروتکل کاربردی تجزیه می کند. یعنی ASIC از مجموعه محدودی از پروتکلهای شبکه پشتیبانی میکند که بستهها را بر اساس قوانین خاص و جداول ارسال ارسال میکند. برای برخی از برنامه های سوئیچ، این امکان وجود دارد که بسیاری از ویژگی های پروتکل پشتیبانی شده از ASIC بدون استفاده باقی بمانند، و علاوه بر این، هرگونه نیاز به تطبیق پروتکل های جدید مستلزم ارتقای کامل سخت افزار است. این عدم انعطاف و ناکارآمدی ASIC های با عملکرد ثابت است که ASICهای سوئیچ قابل برنامه ریزی به دنبال رفع آن هستند.

در مقایسه با ASIC با عملکرد ثابت، (مدارهای مجتمع قابل برنامه ریزی ASIC)سوئیچ های قابل برنامه ریزی ASIC طراحی بر اساس معماری سوئیچ مستقل پروتکل حافظه داخلی آن است. با معماری پروتکل حافظه داخلی ، هر مرحله از خط فرمان حافظه تعریف نشده است و نیاز به برنامه نویسی برای تجزیه بسته ها و منطق حمل و نقل عملکرد تطابق خاص دارد. سوئیچ برنامه نویسی ASIC از یک زبان سطح بالا به نام P4 استفاده می کند که به عنوان جایگزینی برای سوئیچینگ عملکرد ثابت توسعه یافته است.بنیاد شبکه باز زبان P4 را به عنوان یک استاندارد تعریف کرده است و پیشرفت را از طریق یک جامعه فعال و رو به رشد P4 هدایت می کند. توسعه P4 و همچنین سایر زبان های برنامه نویسی پردازش بسته، به صفحه داده امکان می دهد کاملاً قابل برنامه ریزی و عمدتاً مستقل از سخت افزار زیرین باشد.

پژوهشگر و نویسنده: دکتر ( افشین رشید)

دکترایِ تخصصی نانو _ میکرو الکترونیک