تراشه زیستی (Bio chip ) ساختار ، عملکرد (دکترای نانو _ میکرو الکترونیک)

پژوهشگر و نویسنده: دکتر ( افشین رشید)

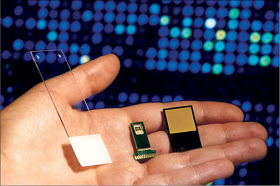

نکته : bio chip حسگر زیستی یا پردازنده زیستی که از فناوری های زیست مدرن و الکترونیک در مقیاس خرد استفاده می کند.Biochips اساساً آزمایشگاه های کوچکی را انجام می دهد که صدها یا بسیاری از پاسخ های بیوشیمیایی همزمان را انجام می دهد. Biochips دانشمندان را قادر می سازد تا مقادیر زیادی برای تجزیه و تحلیل های زنده را به مجموعه ای از اهداف انجام دهند.

Biochip یک نسخه کوچک از آزمایشگاه است که بیش از صدها واکنش بیوشیمیایی به طور همزمان از آن استفاده می کند. آنها به ویژه برای عملکرد در یک محیط بیولوژیکی ، به ویژه در داخل موجودات زنده طراحی شده اند. این وسیله الکترونیکی نیست. Biochips از میلیون ها حسگر زیستی تشکیل شده است که به عنوان میکرو راکتور برای تشخیص آنالیت های خاصی مانند آنزیم ، پروتئین ، مولکول بیولوژیکی و آنتی بادی استفاده می شود.بیوچیپ دارای پروب های مختلفی مانند DNA ، RNAi ، قطعات پروتئینی و ... است که توسط یک نقطه در تراشه نشان داده می شود. این کاوشگرها با اهداف موجود در نمونه مورد آزمایش اتصال می یابند. به دلیل هیبریداسیون ، تماس بین کاوشگرها و هدف آنها انجام می شود. سپس از اسکنرهای Biochip و نرم افزار تجزیه و تحلیل تصویر ریز آرایه برای شناسایی هدف و کمی سازی سیگنال استفاده می شود. نتایج در سطح آماری بدست آمده و در یک زمینه بیولوژیکی تفسیر می شود.

Bio Chip بیو چیپ ها و تراشه های زیستی در آرایه های ژنی و پروتئینی با اینکه چند سال از شناسایی ساختار و تعیین ردیف کامل ژنوم انسان گذشته است و مشخص شده است ژنوم انسان از ۳ میلیارد نوکلئوتید و حدود ۳۰ هزار ژن تشکیل شده است ولی تحول عمده ای در حل بیماریهای وراثتی و کشف علل بیماریهای مختلف انسان به دلیل پیچیدگی های موجود در ساختار ژنتیکی انسان و عوامل مختلف موثر بر آن صورت نگرفته است.زیرا قبلا تصور بر این بود که یک ژن مسئول یک فعالیت است و متخصصین به بررسی ساختار و عملکرد تک تک ژنها و پروتئین ها بطور جداگانه می پرداختند ولی اینک مشخص شده است در برخی از اختلالات ژن های متعددی نقش دارند و ابشاری از فرایند ها در یک بیماری و یا آسیب های سلولی و بافتی نقش دارند.نتیجه این شد که باید روشی برای بررسی هم زمان ردیف، تنوع، تفاوت ژنی، ساختار و فعالیت ده ها، صدها و هزاران ژنوم پروتئین بطور همزمان ابداع شود .

پژوهشگر و نویسنده: دکتر ( افشین رشید)

دکترایِ تخصصی نانو _ میکرو الکترونیک