_بخش آزمایشگاه میکرو اِلکترونیک FPGA

آزمایش (میکرو تراشه FPGA) قسمت و واحد (GAL و بلوک term logic)

پژوهشگر و نویسنده: دکتر ( افشین رشید)

نکته : (Programable logic array) PLA اولین تراشه قابل برنامه ریزی که برای پیاده سازی مدار منطقی آرایه برنامه پذیر and و یک آرایه برنامه پذیر OR میباشد. دو اشکال عمده، هزینه گران ساخت و سرعت پایین آن است .

(Programable array logic) PALتراشه Pal دارای یک آرایه and قابل برنامه ریزی و یک آرایه OR تثبیت شده است.GALتراشه GAL دارای یک آرایه and قابل برنامه ریزی و یک آرایه OR تثبیت شده است. تراشه GAL دارای سرعت بیشتر نسبت به تراشه PAL میباشد.بعد از تراشههای فوق MPGAها و FPGAها به بازار آمدند.

MPGA: Mask programable gate array

FPGA: Field programable gate array

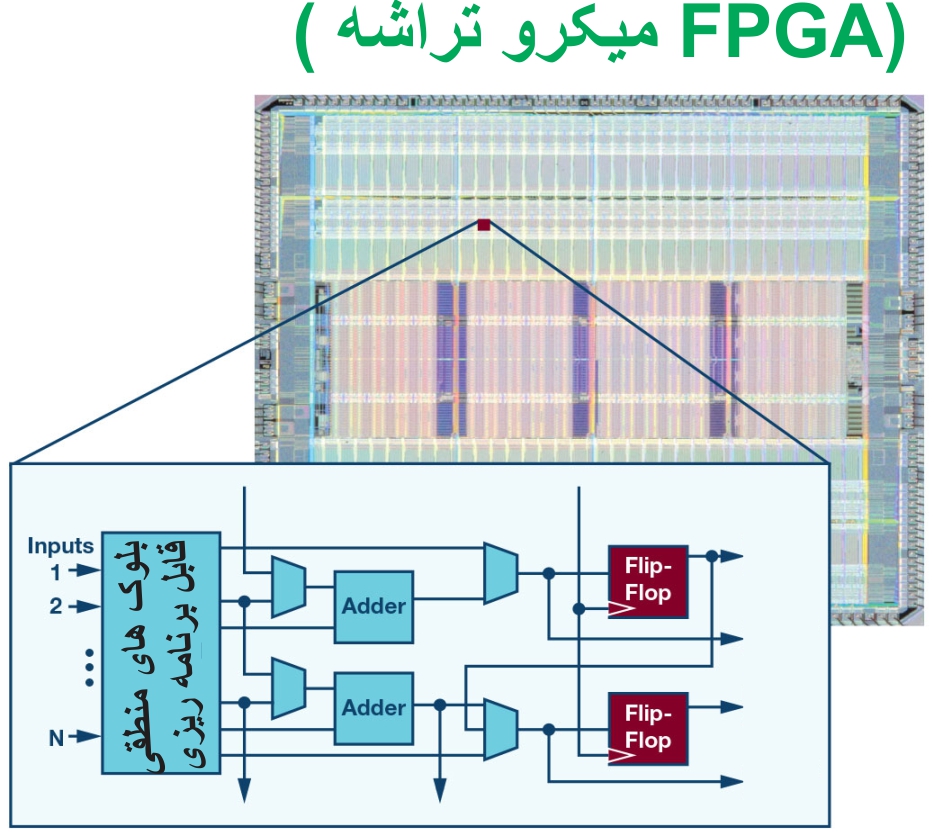

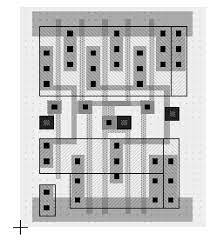

ساختار FPGA

بطور کلی تا کنون سه نوع معماری برای FPGA ها توسط کارخانههای مختلف سازنده ارائه شده است که عبارتند از:

۱-آرایه دو بعدی متقارن Symetric matrix

۲-آرایههای سطری row based

۳-دریایی از گیتها sea of gates

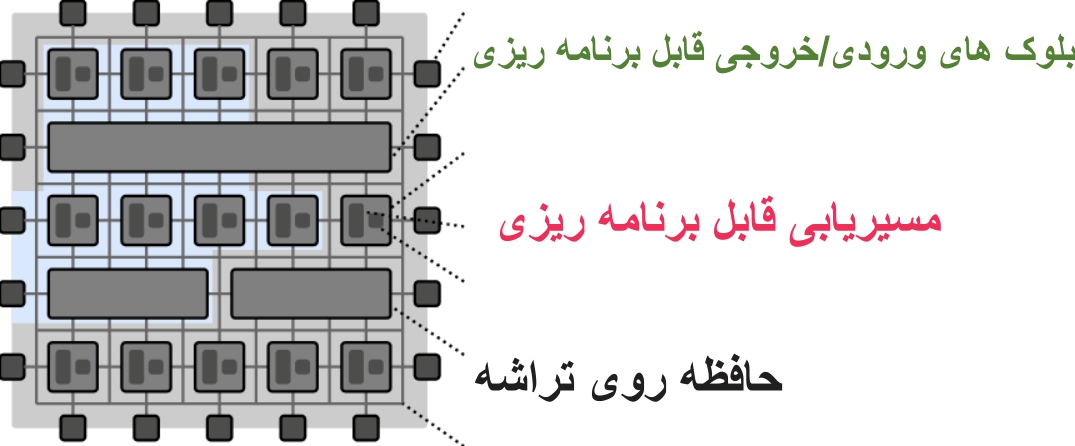

بلوکهای FPGA

۱-بلوکهای منطقی (Logic array Block) LAB

۲-بلوکهای کنترل کننده I/o

۳-اتصالات قابل برنامهریزی PIA

(Programable Interconnect array)

بلوکهای منطقی

بلوکهای منطقی شرکتهای سازنده FPGA از نظر اندازه ومنطق به کار رفته در آنها با هم تفاوتهای بسیاری دارند.

این بلوکها در FPGAها و CPLDهای Altera به نام LAB شناخته میشوند.

هر LAB میتواند شامل سه زیر بلوک Macrocell و Interconnect local و term logic باشد.

بلوک term logic

در LAB برای برقراری ارتباط یک Macrocell با Macrocellهای دیگر ونیز فیدبک به ورودی Macrocell از بلوک term logic استفاده میشود.یک بلوک term logic از دو نوع آرایش بسط دهنده موازی (parallel Expanders) وبسط دهنده عمومی (common Expanders) برای برقرای ارتباط استفاده میکند.بلوکهای کنترل کننده I/o این بلوکها نوعی مدارات منطقی میباشند که وظیفه برنامهریزی نوع پورت خروجی و نیز برقراری فیدبک از پینها به درون PIA را دارد.

پژوهشگر و نویسنده: دکتر ( افشین رشید)

دکترایِ تخصصی نانو _ میکرو الکترونیک