تاریخچه و معرفی برنامه نویسی مدار های الکترونیکی بر مبنای میکروکنترلرهای AVR نرم افزار بسکام (BASCOM) برق _ الکترونیک (آشنایی مقدماتی)

پژوهشگر و نویسنده: دکتر ( افشین رشید)

نکته : برای طراحی و برنامه نویسی مدار های الکترونیکی بر مبنای میکروکنترلرهای AVR از نرم افزار بسکام (BASCOM) استفاده می شود که توسط مارک آلبرتز برنامه نویسی و توسعه داده می شود.

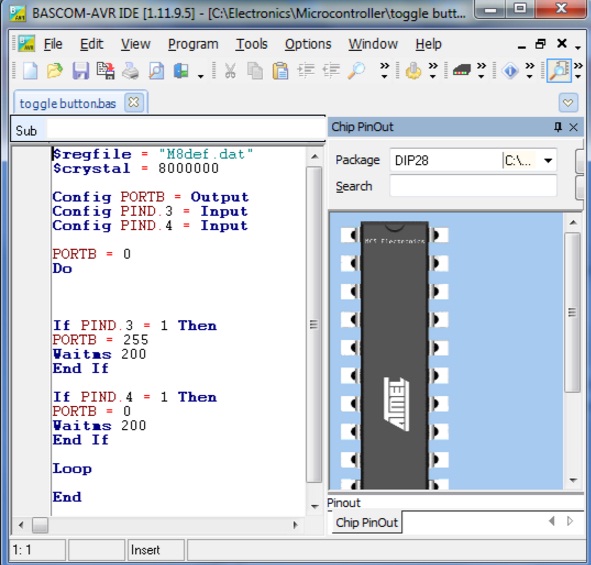

با استفاده از نرم افزار BASCOM به راحتی می توان با کمک IC های خانواده AVR مدارات قابل انعطاف و پیشرفته ایی را بوجود آورد. این نرم افزار در مقایسه با سایر نرم افزار هایی که برای برنامه نویسی IC ها وجود دارد، از لحاظ قدرت، انعطاف پذیری ، آسانی مخصوصا برای کاربران مبتدی و آماتور نسبت به آن ها برتری دارد و بیشتر مورد قرار گرفته است. یکی از مهمترین ویژگی ها و خصوصیات میکروکنتلرلر ها ی AVR برنامه پذیر بودن آن است یعنی به خودی خود قادر به انجام کاری نمی باشد بنابراین نیاز به این دارد که دستوراتی را از طرف ما دریافت کند ، این دستورات به میکروکنترلر می گویند که چگونه از قسمت ها و امکانات داخل خود در جهت هدفی معین که ما تعیین کرده ایم استفاده کند. مجموعه این دستورات همان برنامه نویسی میکروکنترلر های AVR هستند.

آشنایی با محیط نرم افزار بسکام (BASCOM) و منوهای (هدر باکس) File ؛Edite وView

از زبان های برنامه نویسی بیسیک (BASIC) و سی (C) برای برنامه نویسی میکرو کنترلرها استفاده می شود که هر کدام از این زبان ها نیز کامپایلر مخصوص به خود را دارا می باشند. نرم افزار BascomAVR یکی از کامپایلرهای خوب برای برنامه نویسی به زبان بیسیک برای AVR است این نرم افزار که در واقع از زبان برنامه نویسی BASIC استفاده می کند قابلیت های زیادی از ابتدای برنامه نویسی و کامپایل و تولید فایل HEX تا پروگرام کردن برنامه بر روی میکرو را داراست. همچنین در نسخه های جدید این کامپایلر امکان برنام نویسی برای میکروکنترلر های XMEGA نیز فراهم شده است. همچنین پروگرامر محبوب usbasp نیز در این کامپایلر پشتیبانی می شود و می توان مستقیما از داخل کامپایلر میکروکنترلر خود را برنامه ریزی کنید.

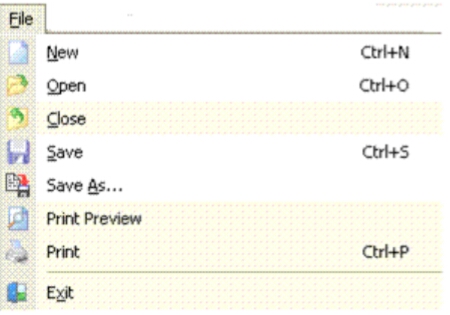

منوی file که دارای گزینه های زیر است:

1-New: با زدن این گزینه یک صفحه جدید برای نوشتن برنامهجدید باز میشود ؛ این صفحه مجهز به ویرایشگر دستورات می باشد؛ یعنی در صورتی که دستوری درست وارد شود به رنگ ابی درمیاید ولی اگر دستور اشتباه باشد به رنگ معمولی (مشکی )است(این مورد برای تعداد زیادی از دستورات اجرا نمی شود) .

2-open: با زدن این گزینه می توانید برنامه ای را که از قبل ذخیره کرده اید باز کنید(برنامه ها با پسوند bas .ذخیره میشوند ،شما همچنین میتوانید برنامه خود را در داخل برنامه های ویرایشگر دیگر مانند Notepad بنویسید و از این پنجره ان راباز کنید ).

3-Close: با انتخاب این گزینه پنجره ای آه برای نوشتن برنامه باز شده ؛ بسته میشود. در صورتی که شما صفحه برنامه را که در پنجره جدید نوشته اید ذخیره نکرده باشید ، از شما در مورد ذخیره کردن برنامه سوال میشود.

4-Save و as Save: این دو گزینه برای ذخیره آردن پروژه به کار میروند.

5-Preview Print وPrint: این دو گزینه برای چاپ آردن برنامه استفاده میشوند با زدن گزینه Preview Print میتوانید نسخه قابل چاپ را قبل از چاپ مشاهده آنید.

6-Exit: با زدن این گزینه برنامه بسکام به طور کامل بسته می شود ؛ اما اگر برنامه شما ذخیره نشده باشد ؛در مورد ذخیره برنامه از شما پرسیده میشود.

7-زیر گزینه Exit: چند گزینه دیگر وجود دارد که این گزینه ها برای دسترسی سریع به اخرین فایل های که باز بوده اند می باشد. برای هر کدام از گزینه ها کلید های میانبری وجود دارد که در کنار گزینه نوشته شده است.

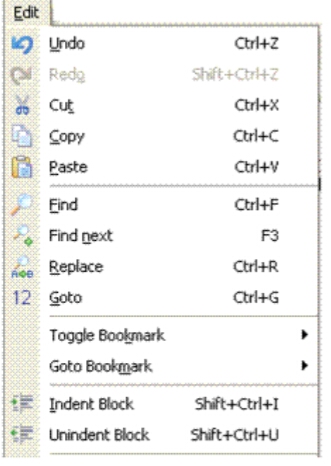

منوی Edite که دارای گزینه های زیر است:

1-UndoوRedo: این دو گزینه برای دست یابی به اخرین تغییرات انجام شده می باشد.

2-CopyوCutوPaste: این سه گزینه برای برداشتن یا آپی آردن قسمتی از متن به جای دیگر میباشد.

3 -Findnext وFind: این دو گزینه برای پیدا آردن قسمتی از متن در برنامه می باشد. نحوه عملکرد آن به این صورت است که بعد از انتخاب گزینهFind ، پنجره جدیدی باز می شود که باید در قسمت find to Text متن مورد نظر را تایپ کنید. بعد روی ok آلیک آنید تا متن مورد نظر در برنامه انتخاب شود .Findnext متن های آن در خط های بعدی برنامه وجود داردپیدا میکند.

4-replace: با این گزینه شما می توانید متنی را جایگزین متن موجود در برنامه نمایید، یعنی در قسمت find to text متن یا کلمه مورد جستجو که باید توسط متن یا کلمه دیگری جایگزین شود را تایپ کنید و در قسمت wath replace متنی را که باید جایگزین شود تایپ می کنیم .دو گزینه بعدی برای گذاشتن علامت در خطوط مختلف و پرش به انها می باشد.

5-IndentBlock وUnindentBlock: این دو گزینه متن انتخاب شده را به اندازه یک tab به چپ یا راست منتقل میکند.

منوی view که دارای گزینه های زیر است:

1-layout Pin : با انتخاب این گزینه پنجره ای باز میشود ، که در ان پایه های میکرو مورد استفاده و شکل ان اورده شده است ، با بردن موس روی هر پایه نقش ان در زیر تصویر نوشتهمیشود.

2 -veiwer pdf :با انتخاب این گزینه شما میتوانید مشخصات میکرو مورد استفاده را ببینید( شما ابتدا باید آن ها را دانلود کنید ، با کلیک روی گزینه نحوه دانلود به شما گفته میشود ، شما همچنین به برنامه Acrobat Adobe برای بازکردن pdf ها نیاز دارید.)

3 -panel error :با انتخاب این گزینه پنجره ی خطاها باز میشود ، این پنجره بعد از کامپایل کردن برنامه ، در صورت وجود خطا خودکار باز میشود.

4-tip : با زدن این گزینه پنجره ای باز میشود که حاوی نکاتی برای بهتر کار کردن با بسکام است.

هارد و BIOS در میکروکنترلرها به اسم و شکل دیگری بیان می شود. به آنها EPROM یا EEPROM می گویند که این ها کار هر دو مورد یعنی هارد و بایوس را انجام می دهند.

پژوهشگر و نویسنده: دکتر ( افشین رشید)

دکترایِ تخصصی نانو _ میکرو الکترونیک