بخش مدار های ASIC/FPGA _ بلوک های منطقی قابل برنامه ریزی

تفاوت میکرو (مدارهای مجتمع FPGA) با مدارهای مجتمع CPLD (مطلب مهم)

پژوهشگر و نویسنده: دکتر ( افشین رشید)

نکته: در ابتدا، میکرو (مدارهای مجتمع FPGA) بلوک های موجود و چیزهای دیگری را شامل می شدند، اما در برتری حافظه داخلی دمیکرو مدارهای مجتمع پیچیده تر مانند دستگاه های منطقی قابل برنامه ریزی ساده (SPLD) و دستگاه های منطقی قابل برنامه ریزی پیچیده (CPLD) فاصله بین دستگاه های منطقی گسسته و FPGA های سطح ورودی را پر میکنند.

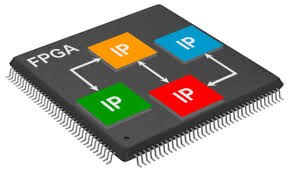

میکرو (مدارهای مجتمع FPGA) سطح ورودی بر مصرف انرژی کم، چگالی منطقی کم و پیچیدگی کم در هر تراشه تاکید دارند. دستگاه های با عملکرد بالاتر بلوک های کاربردی را اضافه می کنند که به عملکرد های خاص اختصاص داده شده اند: به عنوان مثال میتوان به اجزای مدیریت ساعت، حلقه های قفل شده فاز (PLL)، سریال سازها و سریا ل سازهای پرسرعت، MACهای اترنت، کنترل کنندههای PCI express و فرستنده گیرنده های سرعت بالا اشاره کرد. این بلوک ها را می توان با CLBها (که IP نرم نامیده می شوند) پیاده سازی کرد یا به عنوان مدارهای جداگانه طراحی کرد. یعنی IP سخت. بلوک های IP سخت به قیمت پیکربندی مجدد، کارایی را به دست می آورند.

در بالاترین سطح، خانواده میکرو (مدارهای مجتمع FPGA) شامل قطعات پیچیده سیستم روی تراشه (SoC) است که معماری FPGA، IP سخت و یک هسته CPU ریزپردازنده را در یک جزء واحد یکپارچه می کند. در مقایسه با دستگاه های جداگانه، یک SoC FPGA یکپارچگی بالاتر، قدرت کمتر، اندازه برد کوچک تر و ارتباط با پهنای باند بالاتر بین هسته و سایر بلوک ها را فراهم می کندیک طراحی مبتنی بر میکرو (مدارهای مجتمع FPGA) با تعریف وظایف محاسباتی مورد نیاز در ابزار توسعه شروع میشود، سپس آنها را در یک فایل پیکربندی که حاوی اطلاعاتی در مورد نحوه اتصال CLB و سایر ماژول ها است، کامپایل می کند. این فرآیند شبیه چرخه توسعه نرم افزار است با این تفاوت که هدف، معماری خود سخت افزار است نه مجموعه ای از دستورالعمل ها برای اجرا بر روی یک پلت فرم سخت افزاری از پیش تعریف شده است.

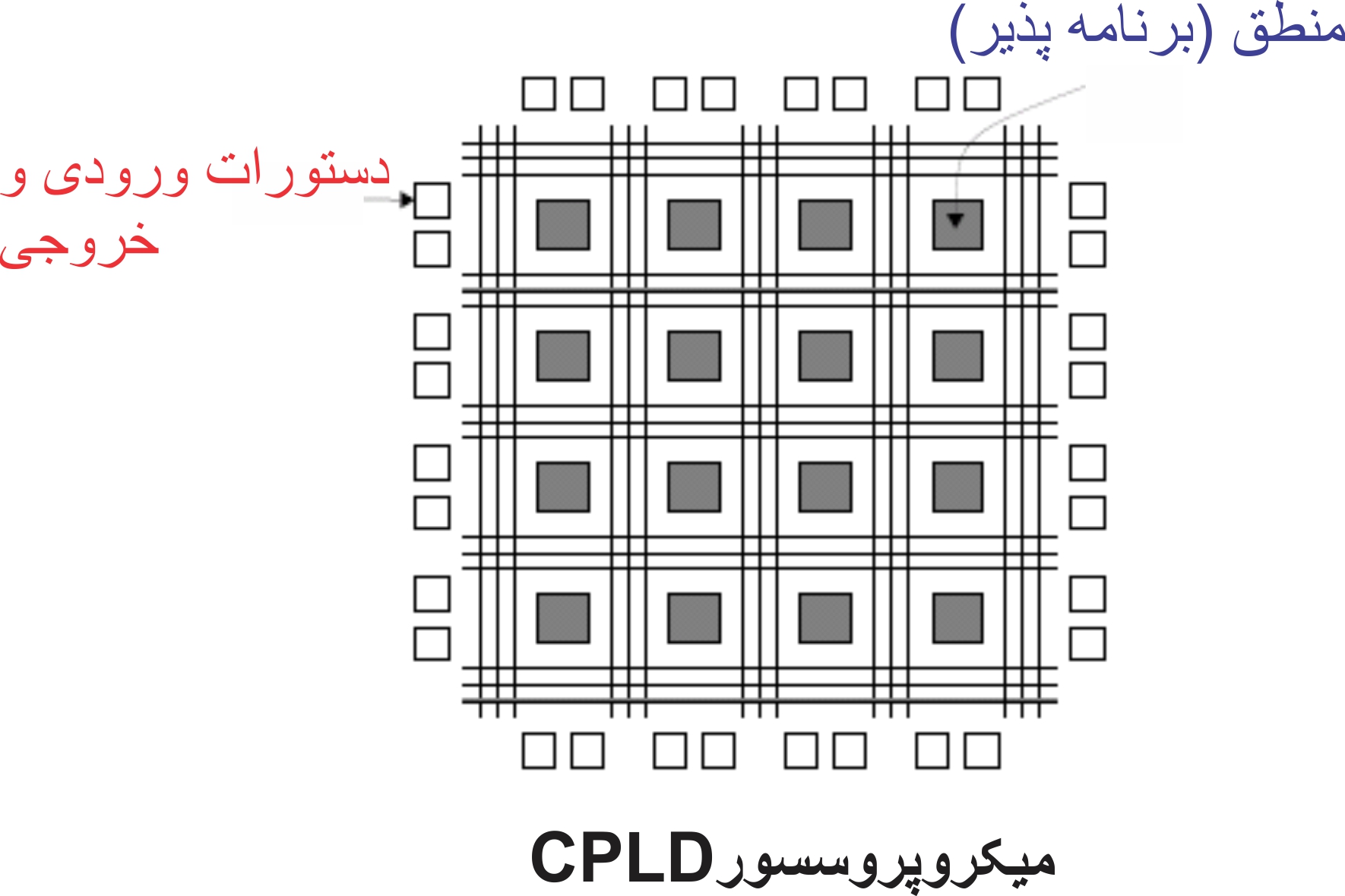

نکته: یک میکروپروسسور CPLD از سه جزء اصلی تشکیل شده است: یک بلوک منطقی ، یک کانال اتصال قابل برنامه ریزی و یک بلوک I/O .

بلوک منطقی درمیکروپروسسور CPLD شبیه یک PLD در مقیاس کوچک است. معمولاً یک بلوک منطقی شامل 4 تا 20 ماکروسل است که هر کدام از آنها به طور کلی از یک آرایه اصطلاح محصول، تخصیص عبارت محصول و ثبات های قابل برنامه ریزی تشکیل شده است. هر ماکروسل دارای تنظیمات متعددی است و هر ماکروسل را می توان به صورت آبشاری استفاده کرد، به طوری که منطق ترکیبی پیچیده تر و توابع منطق زمان بندی را می توان تحقق بخشید. برای CPLD های بسیار یکپارچه، بلوک های آرایه جاسازی شده با RAM/ROM روی تراشه معمولا ارائه می شود.کانال های اتصال قابل برنامه ریزی شبکه های ارتباطی بین بلوک های منطقی، ماکروسل ها و پین های ورودی/خروجی را فراهم می کنند. بلوک های ورودی/خروجی (بلوک های I/O) رابط بین منطق داخلی به پین های ورودی/خروجی دستگاه را فراهم می کنند.

میکروپروسسور CPLD در ساختار ماتریس چند آرایه ای، هر ماکروسل دارای یک آرایه قابل برنامه ریزی و یک آرایه ثابت و همچنین یک فلیپ فلاپ قابل تنظیم با عملکردهای ساعت، فعال کردن ساعت، پاک کردن و بازنشانی مستقل قابل برنامه ریزی است. چندین قسمت همزمان از طریق PIA آرایه اتصال قابل برنامه ریزی و گذرگاه سراسری متصل می شوند. هر قسمت همچنین به ماژول کنترل I/O مربوطه متصل است تا کانال های ورودی و خروجی مستقیم را ارائه دهد.میکروپروسسور CPLD یک دستگاه منطقی قابل برنامه ریزی پیچیده (CPLD) یک دستگاه منطقی با آرایه های AND/OR و ماکروسل های کاملاً قابل برنامه ریزی است. ماکروسلها بلوکهای اصلی یک CPLD هستند که شامل عملیات منطقی پیچیده و منطق برای پیادهسازی عبارات (فرم نُرمال مُنفک) یا به اصلاح قابل انفِکاک هستند. آرایه های AND/OR کاملاً قابل برنامه ریزی مجدد هستند و وظیفه انجام توابع منطقی مختلف را بر عهده دارند. ماکروسل ها را همچنین می توان به عنوان بلوک های عملکردی که مسئول اجرای منطق ترتیبی یا ترکیبی هستند تعریف کرد.

پژوهشگر و نویسنده: دکتر ( افشین رشید)

دکترایِ تخصصی نانو _ میکرو الکترونیک