_CPLD Integrated Circuits Department

The structure and architecture of CPLD or abbreviated complex programmable logic device in (microprocessors and chips)

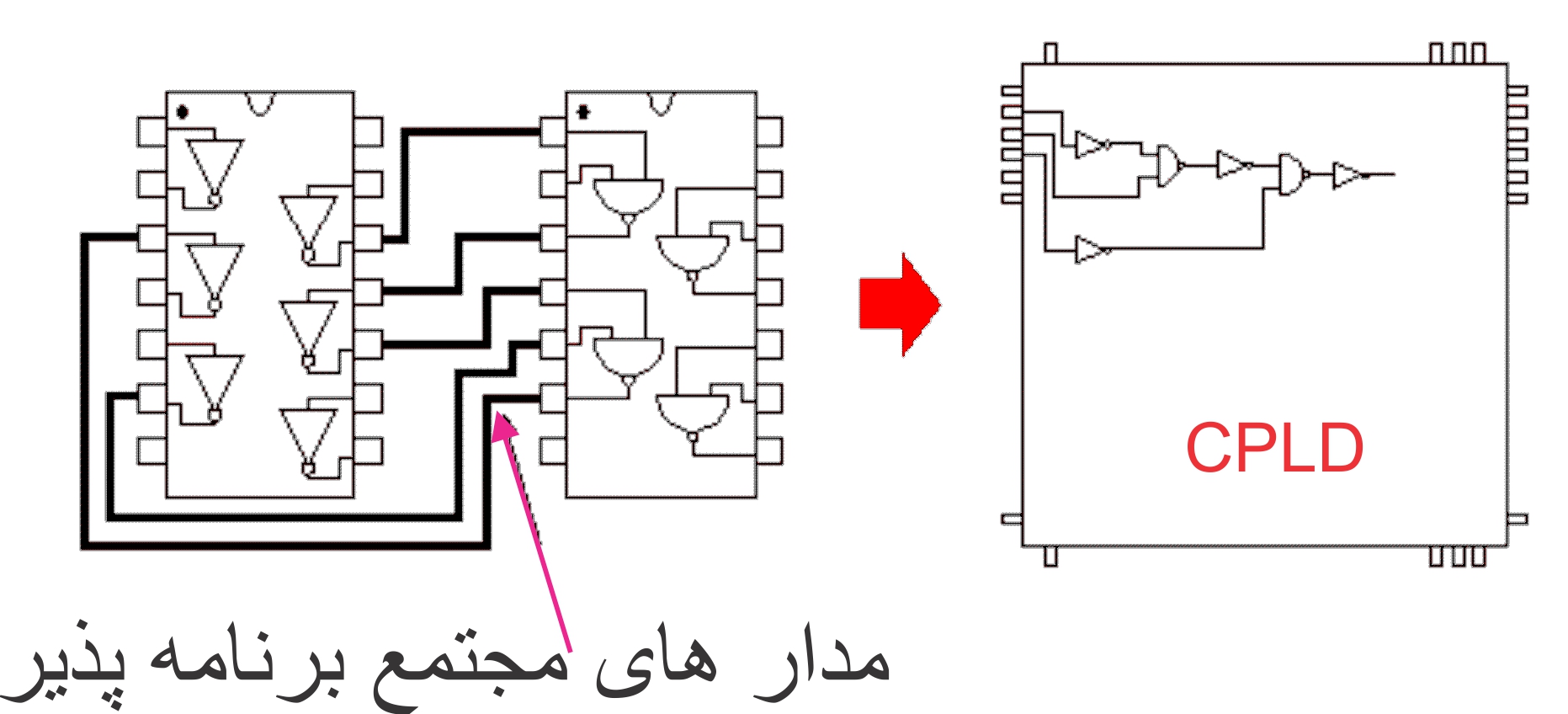

Note: The meaning of CPLD is abbreviated as complex programmable logic device and they are the simplest programmable chips. Compared to FPGAs, this category is much smaller and simpler. But the technology of making them is based on fuses, which means that there is no need for memory for program storage and program loading time.

In general, CPLDs are suitable for implementing small logic circuits. CPLDs are also very energy efficient. In addition to digital functions, some CPLDs have analog features. The most common analog feature is programmable liner speed and drive power on each output pin, allowing the engineer to set slower speeds on low-pressure pins that would otherwise spin unacceptably. and sets stronger and faster rates on high-load pins in high-speed channels. Otherwise it will be too slow.

A CPLD (complex programmable logic device) is a programmable logic device that consists of several simple PLDs (SPLDs) and has a programmable switching matrix between the logic blocks. It has the characteristics of PAL and FPGA architecture, but is more complex than FPGA. A cell macro is the building block of CPLD, which includes regular expressions and regular expressions and more logical operations. The main differences between CPLD and FPGA are architectural.

CPLD has a limiting structure which results in less flexibility. FPGA architectures are interconnected, which makes them not only much more flexible, but also much more complex to design.

Researcher and author: Dr. ( Afshin Rashid)

Specialized doctorate in nano-microelectronics