_بخش مدار های مجتمع CMD (پایه خرچنگی) از نوع HCPLD و CPLD یا (ساختمان گُسسته)

بررسی و تحلیل بسته بندی ic های (SMD) از نوع HCPLD

پژوهشگر و نویسنده: دکتر ( افشین رشید)

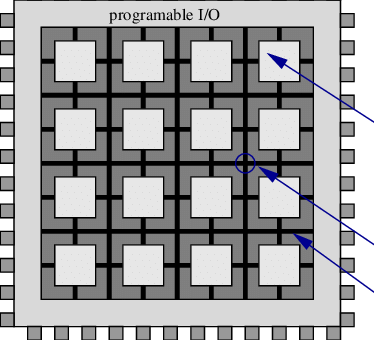

نکته: (High – Capacity – PLD (HCPLD بیشتر از ۶۰۰ گیت قابل استفاده دارند و شامل CPLD و FPGA میشوند.FPGAها ساختمان اتصالات داخلی گسسته دارند، در حالیکه CPLDها دارای اتصالات داخلی پیوسته میباشند.در ساخت HCPLD ها از تکنولوژی EEPROM , EPROM , Sram و Anti – Fuse استفاده شده است.

یک مدار مجتمع یا IC ، تراشه کوچکی است که می تواند به عنوان تقویت کننده ، نوسان ساز ، تایمر ، ریز پردازنده یا حتی حافظه رایانه عمل کند. IC یک ویفر کوچک است که معمولاً از سیلیکون ساخته شده است و می تواند در هر جایی از صدها تا میلیون ها ترانزیستور ، مقاومت و خازن نگه دارد. این الکترونیک های بسیار کوچک می توانند محاسبات را انجام داده و داده ها را با استفاده از فناوری دیجیتال یا آنالوگ ذخیره کنند.

IC های دیجیتال از دروازه های منطقی استفاده میکنند ، که فقط با مقادیر آن و صفر ها کار می کنند. سیگنال کم ارسال شده به یک مؤلفه در IC دیجیتال ، مقدار 0 را در پی خواهد داشت ، در حالی که سیگنال بالا مقدار 1 را ایجاد می کند. IC های دیجیتال نوعی است که معمولاً در رایانه ها ، تجهیزات شبکه و اکثر لوازم الکترونیکی مصرفی پیدا خواهید کرد.IC های آنالوگ یا خطی با مقادیر مداوم کار می کنند. این بدان معناست که یک مؤلفه در یک IC خطی می تواند مقدار دیگری از خود بگیرد و مقدار دیگری را نیز تولید کند. اصطلاح خطی از آنجا استفاده می شود که مقدار خروجی یک تابع خطی از ورودی است. به عنوان مثال ، یک مؤلفه در IC خطی ممکن است مقدار ورودی را با ضریب 2.5 ضرب کرده و نتیجه را حاصل کند. آی سی های خطی معمولاً در تقویت فرکانس صوتی و رادیویی استفاده می شوند. (High – Capacity – PLD (HCPLD بیشتر از ۶۰۰ گیت قابل استفاده دارند و شامل CPLD و FPGA میشوند.FPGAها ساختمان اتصالات داخلی گسسته دارند، در حالیکه CPLDها دارای اتصالات داخلی پیوسته میباشند.در ساخت HCPLD ها از تکنولوژی EEPROM , EPROM , Sram و Anti – Fuse استفاده شده است.

پژوهشگر و نویسنده: دکتر ( افشین رشید)

دکترایِ تخصصی نانو _ میکرو الکترونیک