ترانزیستور اثر میدان تونلی باند به باند (TFET) ساختار و عملکرد ها

پژوهشگر و نویسنده: دکتر ( افشین رشید)

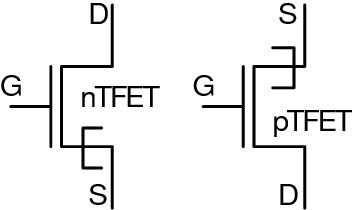

نکته : شِبهِ ترانزیستور تونل اثر میدانی ترانزیستور (TFET) یک نوع تجربی ترانزیستور می باشد. حتی اگر ساختار آن بسیار شبیه به یک ترانزیستور تأثیر میدان نیمه هادی فلزی- اکسید (MOSFET) باشد ، مکانیسم اساسی تعویض در این دو ترانزیستور با یکدیگر فرق می کند ،TFET ها به جای تعدیل انتشار تیرمونیک بر روی یک سد ، مانند MOSFET های سنتی ، با تعدیل تونل کوانتومی از طریق یک سد تغییر می کنند.

ترانزیستور تونلینگ اثر میدانی (TFET)، به عنوان یک جایگزین برای CMOS معمولی به وسیله ی فعال کردن منبع تغذیه ولتاژ (VDD) با مصرف توانی فوق العاده کم، محاسبات کارآمد انرژی، در طی دامنه ی زیر- حد آستانه ی (sub-threshold slope: SS) به وجود آمد. آن نوع دستگاه، یک ساختار بایاس معکوس گیت دار است که معمولا به آن ترانزیستور اثر میدانی تونلی (TFET) می گویند. برای کاربردهای توان پایین، TFET مورد توجه قرار گرفته است. این افزاره نسبت به MOSFET ، جریان نشت استاتیک کمتری دارد و در مقابل SCEs مقاوم تر است. برجسته ترین ویژگی TFET ها ، ظرفیت تولید یک سویینگ آستانه فرعی معکوس (SS) کمتر از mV60/decade حد گرمایی (در 300 کلوین) مربوط به MOSFET های حالت معکوس متداول می باشد. ss شبه حرارتی، قابل حصول است، زیرا جریان درین در TFET ها بوسیله تزریق حامل از سورس به کانال تولید می شود که این غالبا تحت شعاع تونل زنی باند به باند مکانیک کوانتوم (BTBT) قرار می گیرد.

سرعت ترانزیستور TFET متناسب با جریان است. هرچه جریان بیشتر باشد ، ترانزیستور سریعتر قادر به میزان تقویت و شارژ (فشار خازنی متوالی) خواهد بود. برای یک سرعت ترانزیستور معین و حداکثر نشت زیر آستانه قابل قبول ، شیب زیر آستانه بنابراین یک ولتاژ آستانه حداقل را مشخص می کند. کاهش ولتاژ آستانه یک بخش اساسی برای ایده گذاری برای مقیاس گذاری میزان ثابت TFET میباشد. برای غلبه بر برخی چالش های مرتبط با ساختار TFET جانبی، مانند نیاز خود را به پروفایل های دوپینگ فوق العاده تیز؛ با این وجود ، چنین وسایلی به دلیل وجود میدانهای بزرگ عمودی در ساختار ترانزیستور TFET ، ممکن است دچار نشت دروازه شوند.

- پژوهشگر و نویسنده: دکتر ( افشین رشید)

دکترایِ تخصصی نانو _ میکرو الکترونیک