🔬 آز مدارهای اِلکترونیکی

آز (تغذیه مُرکب) بـایـاس تقسـیـم کـنـنـده ولتاژ ( Bias Divider Voltage ) در مدار اِلکترونیکی

پژوهشگر و نویسنده: دکتر ( افشین رشید)

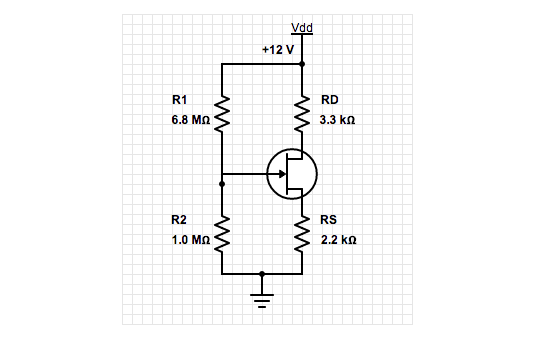

نکته : هــر چنــد در روش خود تغذیه،مقاومــت Rs با ایجــاد فیدبک منفی تا حــدودی موجب پایداری بـایـاس تقسـیـم کـنـنـده( Bias Divider Voltage ) کار FET میشــود.

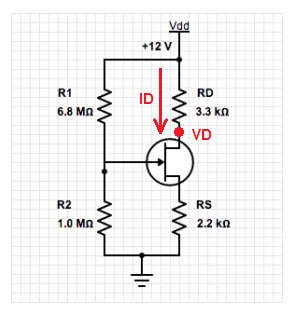

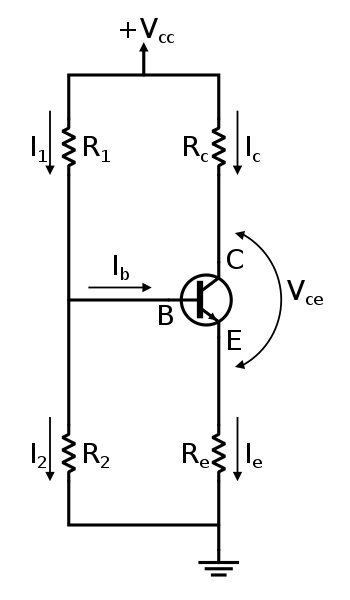

اگر بخواهیم مدار پایــداری بیشترین نقطــه را داشته باشــد، از مداری مطابق بـایـاس تقسـیـم کـنـنـده( Bias Divider Voltage ) استفاده میکنیم. در ایــن مدار به طور همزمان از بایاس تقســیم ولتاژ R١ و R٢ و مدار خود تغذیه (مقاومت RS ) استفاده شده است. به همین دلیل به این تغذیه، تغذیۀ مرکب نیز میگویند.با توجه به اینکه ازگیت ترانزیستور جریانی نمیگذرد، ولتاژ گیت برابر افت پتانسیل در دو سر مقاومت R٢ است به عبارت دیگر VDD بین R١ وR٢ تقسیم ولتاژ میشود و VG از DD به دست میآید. چون این ولتاژ مثبت است،برای این که VGS منفی شود باید پتانسیل سورس یعنی RSID بیشتر از VG باشد تا پیوند گیت سورس در بایاس مخالف قرار گیرد.

ولتاژ مقاومتی با استفاده از منحنی انتقالی مانند تحلیل ترسیمی بایاس سرخود، در مشخصه کار را از طریق ولتاژ مقاومتی نیز میتوان نقطه بایاس تقسیم کنندهٔ انتقالی به دست آورد. در این رسم خط بار روی منحنی مشخصهٔ VGS صفر نیست زیرا مقاومت های نوع بایاس در نقطه ولتاژ افت پتانسیلی در گیت ایجاد مینمایند. لذا در تقسیم کننده عبور این مدار خط بار DC از مبدأ مختصات یعنی از یک نقطه در حلقه خط بار ولتاژ DC در ساختمان ترانزیستور FET ورودی به مدار نمیکند.