Field Effect Nano Transistors (Nano Teransistor Mosfet)

(primary Si/SiGe heterostructure) in field effect nanotransistor

Researcher and author: Dr. ( Afshin Rashid)

Note: Changes in the width of the nano transistor channel due to the field effect of the gate around it can cause undesirable changes and loss of mobility.

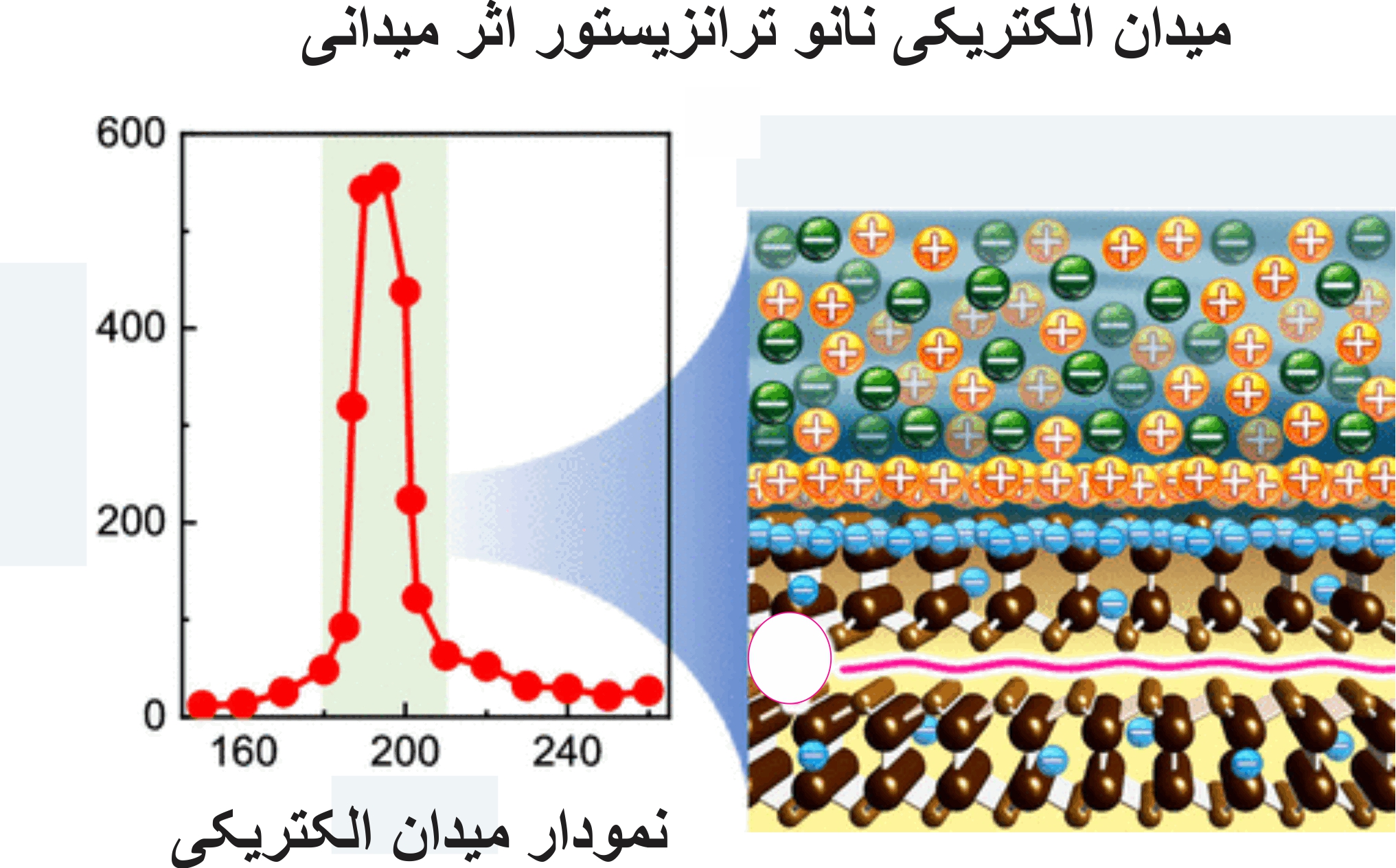

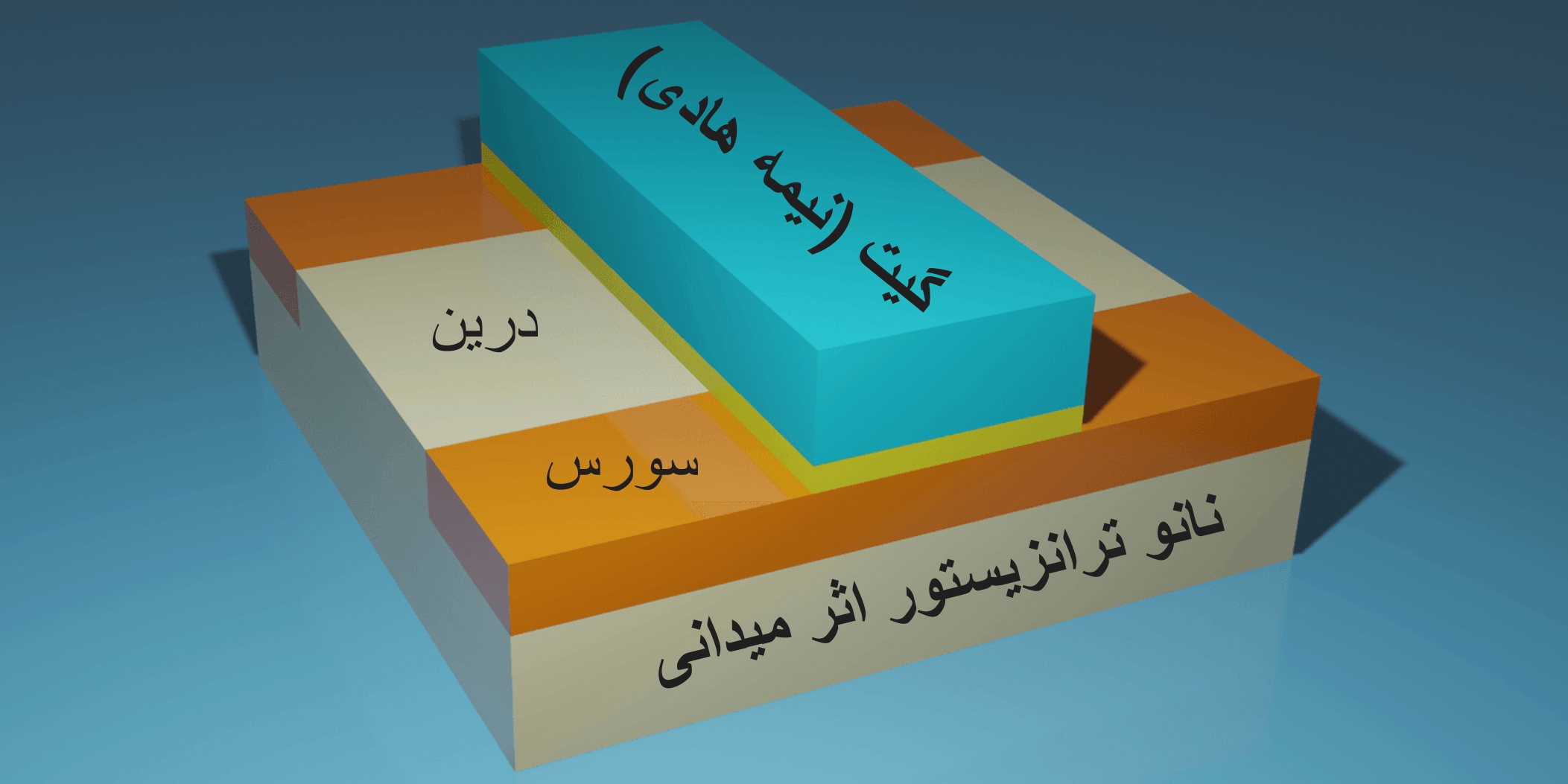

A gate nanotransistor—the gate around the FET—can circumvent the problem. And in terms of electrostatics, an all-gate gate is a nanotransistor in which a gate is placed on all four sides of the channel. It is basically a silicon nanowire around which the gate rotates. In some cases, the surrounding FET can have a common gate or other material in the channels. Horizontally layered nanosheets appear as the consensus for the 5 nm transistor. These devices start with alternating layers of silicon and silicon germanium (SiGe) that are patterned into pillars. The creation of the initial Si/SiGe heterostructure is straightforward and the columnar pattern is similar to the fin structure for nanotransistors. A few for GAAFET nanosheet transistors The indentation in the SiGe layers creates an internal gap between the source/drain, which is eventually located next to the pillar and the space where the gate gate of the nanotransistor is located. This opening distance determines the width of the gate. Then, once the internal spacers are in place, an etch removes the free SiGe channel. The dielectric nano layer places the gate and metal in the spaces between the silicon nanowires. To minimize lattice distortion and other defects, the germanium content of SiGe layers should be as low as possible. The selectivity of the nano layer in the surrounding gate nanotransistor increases with the content of Ge or germanium, and the erosion of the silicon layers during the indentation of the inner gaps or the gate of the nano transistor release channel and the channel affects the thickness of the gate channel around and thus the threshold voltage. putBy reducing all the horizontal and vertical dimensions of the transistor, the electric charge density in different areas of the nano-transistor increases, or in other words, the number of electric charges per unit area of the nano-transistor increases. This event has two negative consequences: First, with the increase in electric charge density, the possibility of electric charge discharge from the insulating areas of the transistor increases , and this event causes damage to the transistor and its failure. This event is similar to the discharge of excess electric charge between the cloud and the ground in the phenomenon of lightning, which causes the ionization of air molecules into negative and positive ions. Secondly , with the increase of the electric charge density, the electrons may leave the range of the radius of one atom and enter the range of the neighboring atom's radius under the influence of repulsive or abduction forces, which have now increased in value.

This phenomenon in nano transistor field effect is called tunneling in quantum physics. Electron tunneling from one atom to the adjacent atom is a phenomenon that happens a lot between electrons in small dimensions. This phenomenon is the basis of the work of some electronic components and some nanoscopes. But in nanotransistor, this phenomenon is not a useful phenomenon, because electron tunneling from one atom to the adjacent atom may continue and cause an electric current. Although this electric current may be very small, but because it is unwanted and unanticipated, it acts as a leakage path for electric current and changes the electrical behavior of the nano-transistor.

Conclusion :

The changes in the nano transistor channel width due to the gate field effect around can cause undesirable changes and loss of mobility.