آزمایش حافظه روی تراشه در مدارهای مجتمع FPGA

پژوهشگر و نویسنده: دکتر ( افشین رشید)

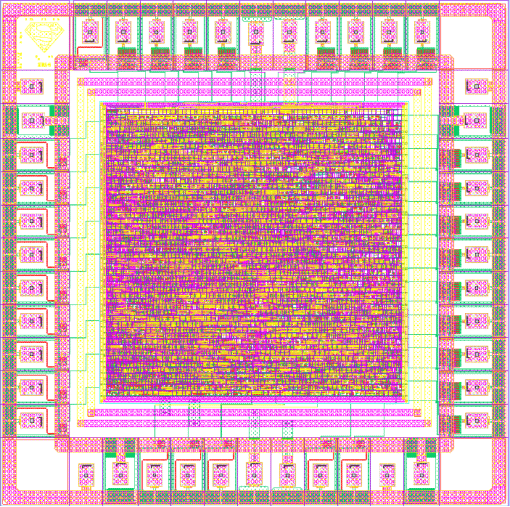

فضای گنجانده شده در بلوک های منطقی میکرو (مدارهای مجتمع FPGA) به عنوان اولین شکل عنصر حافظه روی تراشه در سیستم های FPGA عمل می کند. با این وجود، با بهبود ظرفیت منطق آرایه دروازه قابل برنامه ریزی میدانی، در سیستم های گسترده تری استفاده شد که تقریباً همیشه برای بافر و استفاده مجدد از داده ها روی تراشه به حافظه نیاز داشتند.

از آنجایی که ساخت رَم های بزرگ متشکل از رجیسترها و حافظه اصلی میکرو (مدارهای مجتمع FPGA) حدود 100 برابر چگالی کمتری نسبت به یک بلوک SRAM دارد، نیاز به ذخیره سازی روی تراشه متراکم تر نیز شد.علاوه بر این، نیازهای RAM برنامه های کاربردی اجرا شده بر روی آرایههای دروازه قابل برنامه ریزی میدانی بهطور باورنکردنی متفاوت است.

در بلوک های منطقی میکرو (مدارهای مجتمع FPGA) قبل از زنجیره های حمل شده، تنها مدارهای حسابی اختصاصی مورد استفاده در سیستم های آرایه دروازه قابل برنامه ریزی میدان تجاری، جمع کننده ها بودند. یک منطقه قابل توجه و جریمه تاخیر در نتیجه نیاز به ترکیب چند برابر در منطق نرم با استفاده از حافظه اصلی میکرو (مدارهای مجتمع FPGA) و زنجیره های حمل متحمل شد. با توجه به سهم بازار قابل توجهی از پردازش سیگنال با چگالی ضرب بالا و برنامه های ارتباطی برای آرایه های دروازه قابل برنامه ریزی میدانی، طراحان پیاده سازی های جدیدی را برای رسیدگی به ناکارآمدی پیاده سازی های چند برابر کننده منطق نرم توسعه دادند. این به عنوان پردازش سیگنال دیجیتال یا DSP شناخته می شود.

در بلوک های منطقی میکرو (مدارهای مجتمع FPGA) تکنیک حسابی توزیع شده بدون ضرب یکی از راه های ایجاد طرح های فیلتر پاسخ ضربه محدود یا به اصطلاح (FIR) با استفاده از آرایه های دروازه قابل برنامه ریزی میدان مبتنی برحافظه است. ضرب کننده ها به دلیل رواج آن ها در طراحی های آرایه دروازه ای قابل برنامه ریزی میدانی در دامنه های کاربردی کلیدی و کاهش اندازه، تأخیر و مصرف توان آنها هنگام پیاده سازی در منطق نرم، کاندیدای اصلی برای سخت سازی به عنوان مدارهای تخصصی در سیستم های FPGA هستند.

پژوهشگر و نویسنده: دکتر ( افشین رشید)

دکترایِ تخصصی نانو _ میکرو الکترونیک