_ بخش ترانزیستور(تَک اتصالی) UJTs

بررسی نسبت ذاتی فاصله (η) در ترانزیستور(تَک اتصالی) UJTs

پژوهشگر و نویسنده: دکتر ( افشین رشید)

_60js.png)

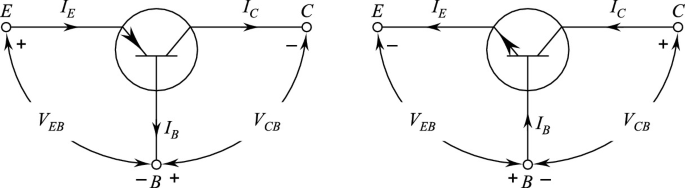

ترانزیستور تک پیوندی (UJT) بر اساس یک مکانیسم منحصر به فرد که با یک ناحیه مقاومت منفی مشخص می شود، عمل می کند که برای کاربرد های آن، به ویژه در نوسان سازهای رلاکسیون، بسیار مهم است. این رفتار توسط ساختار داخلی دستگاه و برهم کنش ولتاژ و جریان در لایه های آن کنترل می شود، که با ترانزیستور های پیوندی دوقطبی (BJT) استاندارد متمایز است.

_nl0.gif)

بررسی نسبت ذاتی فاصله (η) :

این پارامتر برای تعیین ولتاژ آتش (Vp) ترانزیستور تک پیوندی (UJT) بسیار مهم است. این ولتاژ کسری از ولتاژ بین پایه ها است که به صورت R_B1/(R_B1 + R_B2) محاسبه می شود، که در آن R_B1 و R_B2 مقاومت های بین امیتر و پایه های مربوطه هستند.

نسبت ذاتی فاصله (η) در عملکرد UJT نقش اساسی دارد، پارامتری حیاتی که ولتاژ آتش (که به ولتاژ نقطه پیک (Vp) نیز معروف است) را تعیین می کند، ولتاژی که در آن قطعه از حالت خاموش به حالت رسانا تغییر حالت می دهد. پیوند امیتر-بیس UJT رفتاری غیرخطی از خود نشان می دهد که در آن افزایش ولتاژ امیتر فراتر از Vp منجر به کاهش مقاومت امیتر می شود و مشخصه مقاومت منفی فوق الذکر را نشان می دهد.

_3vv6.gif)

چرخه عملکرد UJT با بایاس معکوس پیوند امیتر آغاز می شود که اساساً به عنوان یک سوئیچ باز عمل می کند. هنگامی که ولتاژ در امیتر به ولتاژ نقطه اوج (Vp) می رسد، پیوند امیتر به دلیل مدولاسیون رسانایی میله سیلیکونی، بایاس مستقیم می شود و جریان را به ناحیه بیس تزریق می کند. این گذار باعث می شود UJT وارد حالت رسانایی شود تا زمانی که جریان امیتر به زیر جریان دره کاهش یابد، که در آن نقطه به حالت مقاومت بالای خود باز می گردد. این رفتار چرخه ای همان چیزی است که UJT را برای نوسان سازهای رلاکسیون و مکانیسم های تریگر مناسب می کند.

_slen.png)