بخش مدار های ASIC/FPGA _ بلوک های منطقی قابل برنامه ریزی

(میکرو تراشه FPGA) تجزیه و تحلیل زمان بندی استاتیک

پژوهشگر و نویسنده: دکتر ( افشین رشید)

نکته: انجام دستورات طبقه بندی شده در (میکرو تراشه FPGA) بر اساس تجزیه و تحلیل زمان بندی استاتیک انجام می شود و شواهدی در مورد مسیرهای بحرانی و عملکرد کلی یک میکرو تراشه هوشمند ارائه می دهد.

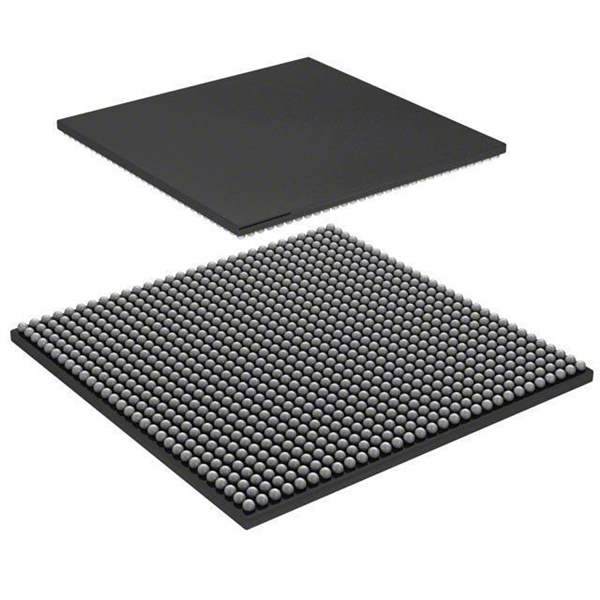

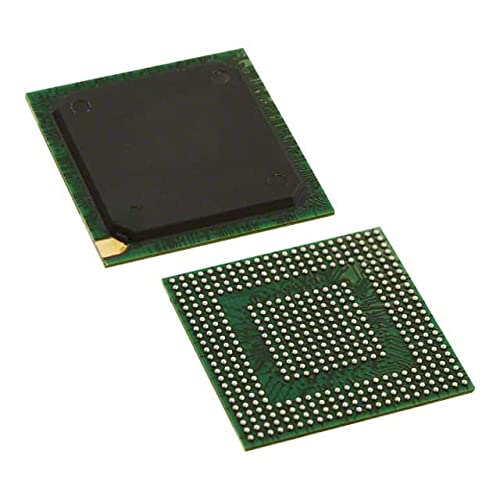

به طور کلی تراشه آرایه دروازه ای با قابلیت برنامه ریزی میدانی (FPGA) یک تراشه/IC نیمه رسانا خاص صنعتی است که بدون نیاز به برنامه ریزی نهایی راه اندازی می شود. مدارها/منطق سخت افزار آن (ماتریس عظیمی از ترانزیستورها، بلوک های منطقی، حافظه ها، ماتریس های اتصال و غیره) قابل برنامه ریزی و تنظیم مجدد توسط "کاربر" با برنامه نهایی مورد نظر است که توسط نرم افزار HDL (زبان توصیف سخت افزار) تعریف شده است.

قابلیت برنامه ریزی مجدد (میکرو تراشه FPGA) باعث می شود که مزایای (پارادایم نرم افزار و پارادایم سخت افزار) در یک تراشه واحد برآورده شوند. فناوری FPGA امکان توسعه عملکردهای پیچیده منطق دیجیتال در سطح مدار / سخت افزار (با قابلیت اطمینان، موازی سازی غیرقابل شمارش، قدرت، سرعت، تأخیر و جبر سخت افزاری) اما با انعطاف پذیری، زمان سریع انجام عملیات دیجیتال، به روز رسانی و تکامل پارادایم نرم افزار را به کاربر می دهد. به عنوان یک توسعه نرم افزار حرفه ای، پیشرفت های FPGA کار آسانی نیست و نیازمند متدولوژی های توسعه کافی و همچنین مهارت ها و دانش قوی در مورد: محاسبات سطح پایین، الکترونیک، برنامه نویسی و وضعیت فن آوری (میکرو تراشه FPGA) است که همچنان ادامه دارد.دامنه کاربرد های (میکرو تراشه FPGA) به دلیل تطبیق پذیری و انعطاف پذیری این دستگاه ها بسیار گسترده است. که کاربرد اصلی پردازش سیگنال دیجیتال FPGA (DSP)، ارتباطات، پردازش داده و غیره است.

انتخاب (میکرو تراشه FPGA) برای کاربرد های پردازش سیگنال به دلیل فرکانس کاری بالا، ظرفیت پردازش موازی آن و غملکرد نسبتاّ پایین آن در مقایسه با ASIC ها است. به طور کلی، منطق یک CPLD برای انجام چنین پردازشی کافی نیست. توانایی پیاده سازی کنترل کننده مبتنی بر FPGA به عنوان یک سیستم Real-Time سخت که میتواند در یک زمان قطعی محاسبه شده به هر زمان تغییر حیاتی در محیط کنترل واکنش نشان دهد. جنبه دیگر امکان پیکربندی مجدد (میکرو تراشه FPGA) در طول زمان اجرا است که با انتخاب بهترین الگوریتم کنترل کننده مناسب، سازگاری با یک محیط در حال تغییر را امکان پذیر می کند، در حالی که منابع منطقی لازم و زمان استقرار را کاهش می دهد.

پژوهشگر و نویسنده: دکتر ( افشین رشید)

دکترایِ تخصصی نانو _ میکرو الکترونیک