بخش مدار های ASIC/FPGA _ بلوک های منطقی قابل برنامه ریزی

میکرو (مدارهای مجتمع FPGA) حاوی بلوک های منطقی قابل تنظیم (CLB)

پژوهشگر و نویسنده: دکتر ( افشین رشید)

میکرو (مدارهای مجتمع FPGA) حاوی بلوک های منطقی قابل تنظیم (CLB) و مجموعه ای از اتصالات قابل برنامه ریزی هستند که به طراح اجازه می دهد بلوک ها را به هم متصل کرده و آنها را برای انجام همه چیز از گیت های منطقی ساده تا توابع پیچیده پیکربندی کند. طرح های SoC کامل حاوی چندین فرآیند را میتوان روی یک دستگاه FPGA قرار داد.

میکرو (مدارهای مجتمع FPGA) بسیار متنوع هستند. آنها به توسعه دهندگان اجازه می دهند تا هر تعداد متغیر را پس از ساخته شدن مدارهای مجتمع آزمایش کنند. در صورت نیاز به تغییرات، فایل های پیکربندی جدید به دستگاه منتقل می شوند که عملکرد جدیدی را در دسترس قرار می دهد. این انعطاف پذیری به حافظه ها اجازه می دهد تا سیستم ها را زودتر در فرآیند طراحی ارسال کنند.

یک مدار مجتمع FPGA طراحی شده است تا ولتاژها را به حداکثر برساند که باعث می شود در برابر نویز و دیگر تداخل های دنیای واقعی به شدت انعطاف پذیر باشند. مفهوم دیجیتال در یک مدار مجتمع FPGA همچنین راهی برای طراحی رفتار پیچیده در مدار بدون نیاز به نگرانی در مورد طراحی سطح پایین به وجود می آورد.میکرو (مدارهای مجتمع FPGA) یک مدار مجتمع است که از بلوک های سخت افزاری داخلی با اتصالات قابل برنامه ریزی توسط کاربر برای سفارشی کردن عملیات برای یک برنامه خاص تشکیل شده است. اتصالات به راحتی قابل برنامه ریزی مجدد هستند و به یک FPGA اجازه می دهد تا تغییرات یک طراحی را انجام دهد یا حتی از یک برنامه جدید در طول عمر قطعه پشتیبانی کند.

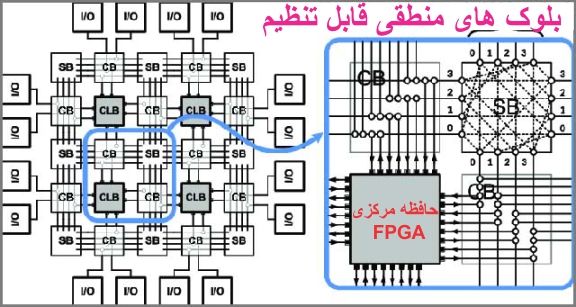

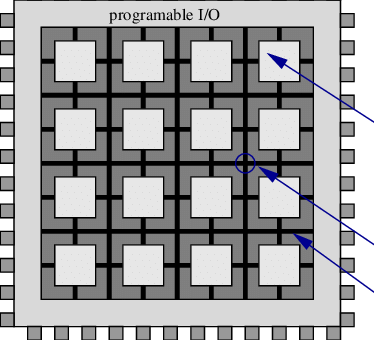

FPGA ریشه در دستگاه های قبلی مانند حافظه های فقط خواندنی قابل برنامه ریزی (PROM) و دستگاه های منطقی قابل برنامه ریزی (PLD) دارد. این دستگاه ها را می توان در کارخانه یا در مدار الکترونیکی برنامه ریزی کرد، اما از فناوری فیوز استفاده می کردند (از این رو عبارت «برنامه ریزی یکبار مصرف PROM») و پس از برنامه ریزی اولیه نمی توان آن ها را تغییر داد. یک معماری پایه FPGA متشکل از هزاران عنصر اساسی به نام بلوک های منطقی قابل تنظیم (CLB) است که توسط سیستمی از اتصالات قابل برنامه ریزی به نام فابریک احاطه شده اند که سیگنال ها را بین CLB ها هدایت می کند. ورودی/خروجی (I/O) رابط بین FPGA و دستگاه های خارجی را مسدود می کند.

پژوهشگر و نویسنده: دکتر ( افشین رشید)

دکترایِ تخصصی نانو _ میکرو الکترونیک