Section _ Understanding (Quartz transistor ) with piezoelectric properties

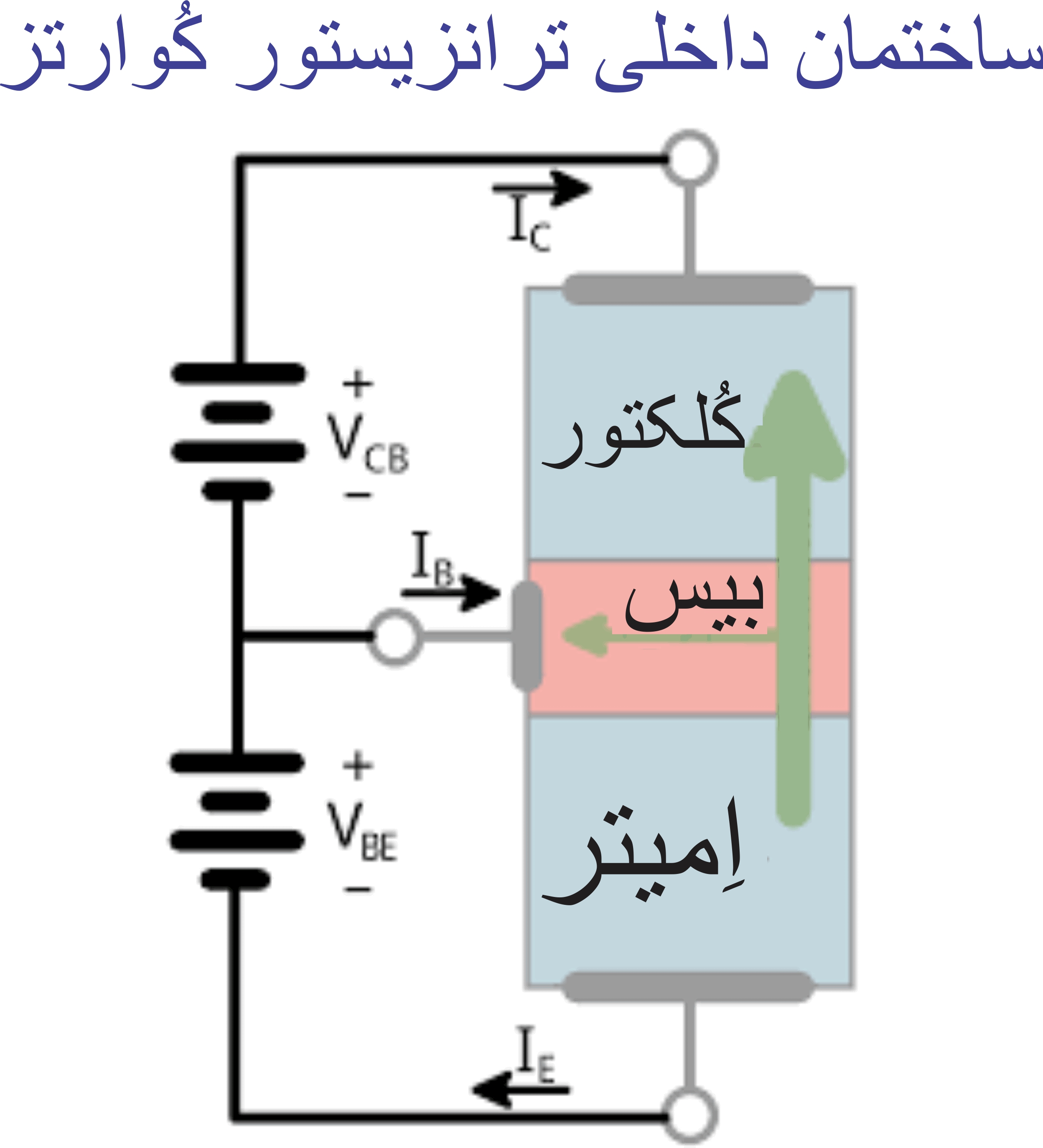

Investigating the internal structure and construction of the Quartz Transistor; with piezoelectric properties

Researcher and author: Dr. ( Afshin Rashid)

Note: The generation of electricity using pressure is called piezoelectricity. The ability to convert mechanical pressure and electricity into each other is called the "piezoelectric property."

Piezoelectricity is the generation of electricity by polarization of a crystal under the application of stress. When an electric field is applied to a piezoelectric crystal, it undergoes strain, which is called inverse piezoelectric behavior.

A necessary condition for a crystal to be piezoelectric is the absence of central symmetry in the crystal structure. Examples of piezoelectric materials are lead-zirconate-titanate compounds PZT with a perovskite structure, ZnO, and quartz.

_ife5.gif)

Piezoelectricity is a property that some crystals, including quartz, produce a voltage when voltage is applied to them or when exposed to mechanical pressure. This property of quartz crystal is used in watches. By applying voltage through the watch battery and considering a certain number of crystal oscillations in one second, the second hand of the watch advances by one second. Another application of quartz, due to its piezoelectric properties, is radio transmitters, radio receivers, and computers. In a way, it can be said that all movable and immovable devices owe their special precision and elegance to this property of quartz. Research shows that if the pendulum inside a bell is made in the form of a quartz crystal and is set in motion, and the so-called bell rings, it will ring for one minute. The truth is that almost no energy will be wasted in this material. If the axes of a quartz bell are exactly aligned with the axes of a single quartz crystal, it will have an oscillating voltage on its surface. What was more interesting was that the amount of this voltage and its fluctuation had nothing to do with temperature.

Internal building:

Quartz , which is composed of silicon and oxygen, is the most common mineral on Earth.

Billions of people use quartz every day, but few of them know about it, because the tiny quartz crystals they use are hidden inside their watches and clocks.

_ But these white or transparent crystals that are found all over the world;

_ Some materials, such as some ceramics and quartz crystals, can generate electricity when subjected to mechanical stress. As mentioned earlier, the ability to convert mechanical stress and electricity into each other is called the "piezoelectric property".

_ Quartz crystals that have this property always vibrate at a certain frequency or frequency with a given electrical voltage. Therefore, these crystals maintain a precise measure of frequency or frequency, which helps regulate the movement of the clock and greatly increases its accuracy.

Application of quartz transistor (piezoelectronics)

Quartz is also used in radios, microprocessors, and many other industrial devices.

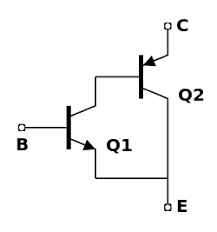

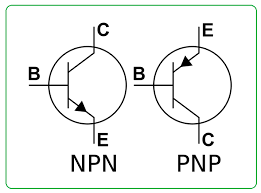

In crystalline structures, the dispersion and spacing of components have a special geometric order that is usually not the same in all directions. Unlike crystals, in amorphous or non-crystalline solids, the dispersion and spacing of their constituent components are the same in all directions. Therefore, some of the physical properties of non-crystalline solids, such as thermal conductivity, light scattering, and electrical conductivity, are also the same in all directions. These non-crystalline solids are called isotropic or isotropic. Because the physical properties of most crystalline solids are different in different directions, they are called anisotropic or anisotropic. Only crystals that crystallize in the cubic system act like non-crystalline bodies; because they have equal dimensions in three spatial directions, the phenomenon of anisotropy causes the appearance of properties in crystals that, due to these properties, find various and important applications in industry. For example, if we pull or press crystals such as quartz or tourmaline from two sides in a direction perpendicular to Pressure or tension causes opposite electrical charges. If we change the direction of this pressure or tension, the type of electrical charge changes, this phenomenon is called piezoelectricity. Heat creates electricity in some crystals, causing one side of them to be positively charged and the opposite side to be negatively charged. As a result, an electric potential difference is created between these two sides. Also, if we connect an alternating electric current to these crystals, the crystals expand and contract alternately and produce sound due to vibration. This property is used to produce sound waves, ultrasonic waves, electrical oscillations, and to make crystal microphones and phonograph needles. Some crystals, such as crystals of the elements germanium, silicon, and carbon, have semiconducting properties and allow electric current to pass through them to some extent. If we heat semiconductor crystals or place them in the path of light, their electrical resistance decreases and they pass electricity better. Semiconductors are used in the electronics and telecommunications industries in the form of diodes, transistors, and other electronic components. A diode or rectifier is made of two pieces of semiconductor crystals and is used to rectify alternating currents. A transistor is made of three pieces of semiconductor crystals and is used to amplify weak currents and rectify alternating currents.

Researcher and author: Dr. ( Afshin Rashid)

Specialized PhD in Nano-Microelectronics