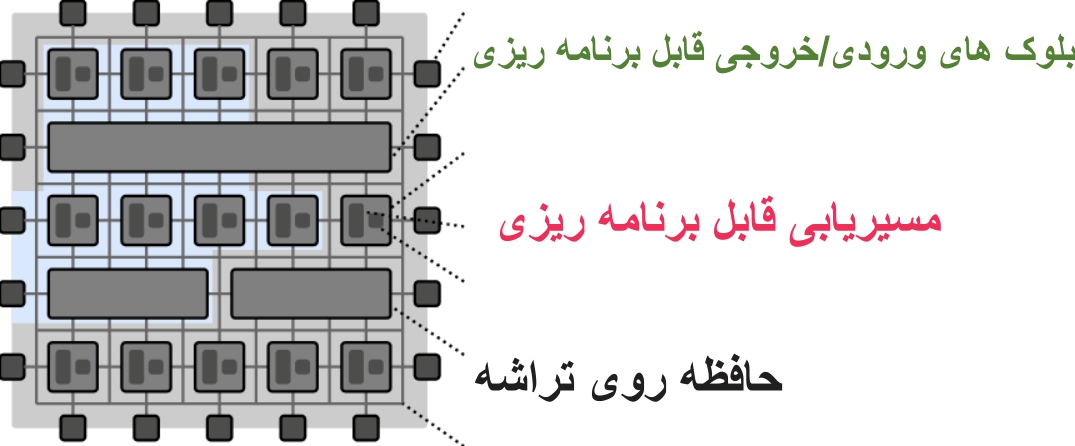

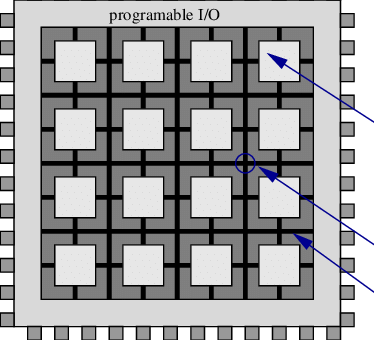

بخش مدار های ASIC/FPGA _ بلوک های منطقی قابل برنامه ریزی

بیت اِستریم و پیکربندی حافظه (میکرو تراشه FPGA)

پژوهشگر و نویسنده: دکتر ( افشین رشید)

اطلاعات پیکربندی در (میکرو تراشه FPGA) در سلول های حافظه پیکربندی ذخیره می شود. به جای استفاده از یک بلوک RAM برای ذخیره سازی، حافظه FPGA در سراسر تراشه در یک شبکه 160×71 توزیع می شود و اطمینان حاصل می کند که هر بیت در کنار مداری است که کنترل می کند. یک بیت استریم پیکربندی در FPGA بارگذاری می شود. جریان بیت به رجیستر شیفتی که از مرکز تراشه (صورتی) میگذرد، تغذیه میشود. هنگامی که 71 بیت در رجیستر شیفت بارگذاری شد، مدار انتخاب ستون خاصی از حافظه را انتخاب می کند و بیت ها به صورت موازی در این ستون بارگذاری می شوند. سپس 71 بیت بعدی در رجیستر shift بارگذاری می شود.این فرآیند برای تمام 160 ستون FPGA تکرار می شود و کل بیت استریم را در تراشه بارگذاری می کند.

از آنجایی که (میکرو تراشه FPGA) به صورت موازی کار می کنند، سرعت بسیار بالاتری دارند و بنابراین می توان از آنها برای حل مسائل پیچیده محاسباتی، همراه با قابلیت برنامه ریزی مجدد استفاده کرد - این باعث می شود(میکرو تراشه FPGA) ها ماشین های قدرتمند و انعطاف پذیر باشند. نکته مهم این است که جریان بیت دقیقاً همانطور که در فایل ظاهر می شود در سراسر تراشه توزیع می شود: چیدمان بیت ها در فایل بیت استریم با طرح فیزیکی روی تراشه مطابقت دارد، هر بیت در (میکرو تراشه FPGA) در کنار مداری که کنترل می کند ذخیره می شود. بنابراین، فرمت فایل بیت استریم مستقیماً با طرح مدارهای سخت افزاری تعیین می شود. به عنوان مثال، هنگامی که بین خطوط حافظه (میکرو تراشه FPGA) به دلیل مدار بافر شکاف وجود دارد، همان شکاف در جریان بیت ظاهر می شود. محتوای جریان بیت حول مفاهیم نرم افزاری مانند فیلدها یا جداول داده یا بلوک های پیکربندی طراحی نشده است.

.

منابع حافظه یکی دیگر از مشخصات کلیدی است که هنگام انتخاب (میکرو تراشه FPGA) باید در نظر گرفته شود. رم تعریف شده توسط کاربر، تعبیه شده در سراسر تراشه FPGA، برای ذخیره مجموعه داده ها یا انتقال مقادیر بین وظایف موازی مفید است. بسته به خانواده FPGA، میتوانید (میکرو تراشه FPGA) را در بلوک های 16 یا 36 کیلوبایتی پیکربندی کنید.الگوریتم های پردازش سیگنال دیجیتال اغلب نیاز به پیگیری کل یک بلوک داده یا ضرایب یک معادله پیچیده و بدون حافظه داخلی دارند (میکرو تراشه FPGA) به قطعات مستقل منطق سخت افزاری اجازه می دهد تا توسط ساعت های مختلف هدایت شوند. انتقال دادهها بین منطقی که با سرعتهای مختلف اجرا میشود میتواند مشکل باشد، و حافظه داخلی اغلب برای صاف کردن انتقال با استفاده از بافرهای حافظه اول استفاده میشود.

در حالی که مزایای بسیاری مانند سرعت، قابلیت اطمینان و انعطاف پذیری برای(میکرو تراشه FPGA) وجود دارد، اما معاوضه هایی نیز با FPGA ها وجود دارد. (میکرو تراشه FPGA) اکوسیستم محرک و پایه کد/IP که معماری های ریزپردازنده و سیستم عامل ها دارند را ندارند. علاوه بر این، ریزپردازندهها همراه با سیستمعاملها، پایهای را برای ساختار فایل و ارتباط با دستگاههای جانبی مورد استفاده برای بسیاری از وظایف، اغلب ضروری، مانند ثبت دادهها بر روی دیسک، فراهم میکنند.در نتیجه، در طول دهه گذشته، یک معماری ترکیبی، که گاهی معماری ناهمگن نامیده میشود، ظهور کرده است که در آن یک ریزپردازنده با یک FPGA جفت میشود که سپس به I/O متصل میشود. FPGA های مدرن اغلب گیت های منطقی را با پردازنده ها در یک تراشه واحد به نام System on Chip (SoC) برای افزایش عملکرد محاسباتی ترکیب می کنند. این رویکرد از مزایایی که هر دو این هدف ارائه می دهند بهره می برد.

پژوهشگر و نویسنده: دکتر ( افشین رشید)

دکترایِ تخصصی نانو _ میکرو الکترونیک