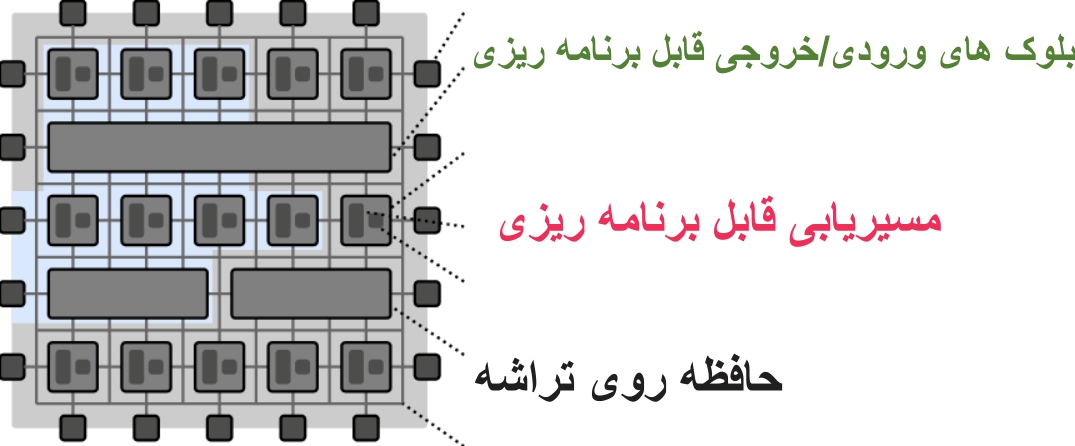

(مدارهای مجتمع FPGA) دارای مسیریابی قابل برنامه ریزی بسیار مهم و کاربردی

پژوهشگر و نویسنده: دکتر ( افشین رشید)

نکته: میکرو (مدارهای مجتمع FPGA) دارای مسیریابی قابل برنامه ریزی بسیار مهم است زیرا معمولاً بیش از پنجاه درصد از سطح (مدارهای مجتمع FPGA) و تأخیر مسیر بحرانی برنامه ها را به خود اختصاص می دهد. مسیریابی قابل برنامه ریزی شامل بخش های سیم پیش ساخته و سوئیچ های از پیش تنظیم شده است. با پیکربندی ترکیب مناسب سوئیچ ها، هر خروجی یک بلوک تابع ممکن است به هر ورودی مرتبط شود. دو نوع اساسی از معماری مسیریابی آرایه دروازه قابل برنامه ریزی میدانی وجود دارد.

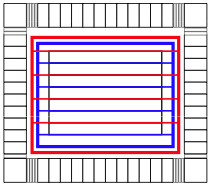

در میکرو (مدارهای مجتمع FPGA) طرح ها ذاتاً سلسله مراتبی هستند. اجزای سطح بالاتر ماژول های سطح پایین تر را نمونه سازی می کنند و سیگنال ها را در سراسر آنها پیوند می دهند، و انگیزه ای برای آرایه های گیت قابل برنامه ریزی سلسله مراتبی فراهم می کنند. آرایه های گیت قابل برنامه ریزی سلسله مراتبی می توانند این اتصالات را با استفاده از سیم های کوتاهی که بخش های مجزای یک تراشه را به هم متصل می کنند، بسازند، زیرا ارتباط بیشتر بین ماژول هایی که در سلسله مراتب طراحی نزدیک به هم هستند اتفاق می افتد. چگالی و عملکرد FPGA تحت تأثیر طراحی مسیریابی است.در میکرو (مدارهای مجتمع FPGA) پین های رابط برای پیوند بلوک های منطقی با اجزای خارجی استفاده می شود. رابط بین آرایه گیت قابل برنامه ریزی میدانی و مدارهای خارجی IOB (بلوک خروجی ورودی)، یک دستگاه ورودی و خروجی قابل برنامه ریزی است که برای برآوردن نیازهای محرک و تطبیق سیگنال های ورودی/خروجی تحت ویژگی های مختلف الکتریکی مورد استفاده قرار می گیرد. بلوک های ورودی/خروجی معماری مسیریابی و (واحد CLB )ها را به عناصر بیرونی متصل می کنند.

در میکرو (مدارهای مجتمع FPGA) بین پین های بسته و مدارهای زیرین دستگاه، بلوک های ورودی/خروجی اتصالات یک طرفه یا دو طرفه قابل برنامه ریزی را فراهم می کنند. اجرای یک برنامه کاربردی مستلزم ساخت مدار از ابتدا بود زیرا آرایه های دروازه قابل برنامه ریزی میدان قبلی فاقد پردازنده ای برای اجرای هر نرم افزاری بودند. در نتیجه، یک FPGA ممکن است به گونهای برنامهریزی شود که مانند یک گیت OR ساده باشد یا مانند یک پردازنده چند هستهای پیچیده باشد.

فضای گنجانده شده در بلوک های منطقی میکرو (مدارهای مجتمع FPGA) به عنوان اولین شکل عنصر حافظه روی تراشه در سیستم های میکرو (مدارهای مجتمع FPGA) عمل می کند. با این وجود، با بهبود ظرفیت منطق آرایه دروازه قابل برنامه ریزی میدانی، در سیستم های گسترده تری استفاده شد که تقریباً همیشه برای بافر و استفاده مجدد از داده ها روی تراشه به حافظه نیاز داشتند. از آنجایی که ساخت رم های بزرگ متشکل از رجیسترها و (فضای برنامه ریزیLUT ها) حدود 100 برابر چگالی کمتری نسبت به یک بلوک SRAM دارد، نیاز به ذخیره سازی روی تراشه متراکم تر نیز شد.

پژوهشگر و نویسنده: دکتر ( افشین رشید)

دکترایِ تخصصی نانو _ میکرو الکترونیک